Arm Unveils 2023 Cell CPU Core Designs: Cortex-X4, A720, and A520

All through the world, if there’s one common fixed within the smartphone and cell machine market, it is Arm. Whether or not it is cell chip makers basing their SoCs on Arm’s absolutely synthesized CPU cores, or simply counting on the Arm ISA and designing their very own chips, on the finish of the day, Arm underlies nearly all of it. That sort of market saturation and relevance is a testomony to all the onerous work that Arm has accomplished in the previous few a long time getting so far, however it’s additionally a grave duty – for many cell SoCs, their efficiency solely strikes ahead as rapidly as Arm’s personal CPU core designs and related IP do.

Consequently, we have seen Arm settle right into a yearly cadence for his or her consumer IP, and this yr is not any exception. Timed to align with this yr’s Computex commerce present in Taiwan, Arm is exhibiting off a brand new set of Cortex-A and Cortex-X sequence CPU cores – in addition to a brand new era of GPU designs – which we’ll see carrying the torch for Arm beginning later this yr and into 2024. These embrace the flagship Cortex-X4 core, in addition to Arm’s mid-core Cortex-A720. and the brand new little-core Cortex-A520.

Arm’s newest CPU cores construct upon the muse of Armv9 and their Complete Compute Answer (TSC21/22) ecosystem. For his or her 2023 IP, Arm is rolling out a wave of minor microarchitectural enhancements via its Cortex line of cores with delicate adjustments designed to push effectivity and efficiency all through, all of the whereas shifting fully to the AArch64 64-bit instruction set. The newest CPU designs from Arm are additionally designed to align with the continued industry-wide drive in the direction of improved safety, and whereas these options aren’t strictly end-user going through, it does underscore how Arm’s generational enhancements are to extra than simply efficiency and energy effectivity.

Along with refining its CPU cores, Arm has undertaken a complete improve of its DynamIQ Shared Unit core complicated block, with the DSU-120. Though the modifications launched are delicate, they maintain substantial significance by way of enhancing the effectivity of the material holding Arm CPU cores collectively, together with extending Arm’s attain even additional by way of efficiency scalability with help for as much as 14 CPU cores in a single block – a transfer designed to make Cortex-A/X even higher suited to laptops.

With three new CPU cores and a brand new core complicated, there’s rather a lot to cowl. So let’s dive proper in.

Arm TCS23 at a Excessive Degree: Pushing Effectivity & Going Pure 64-bit

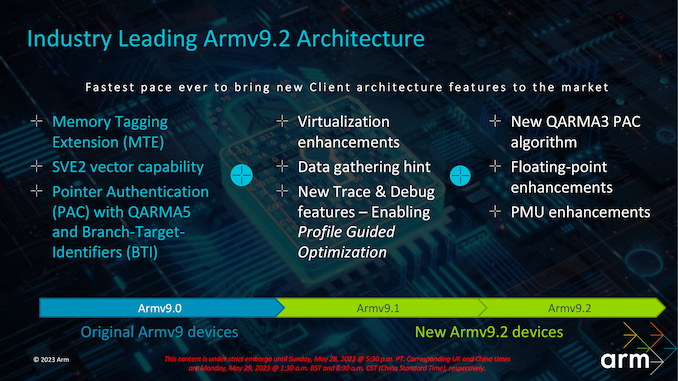

Increasing on the enhancements launched within the Armv9.1 structure final yr, Arm is progressing via its scheduled growth cycle with the newest Armv9.2 structure. The first goal of this cycle is to remove help for 32-bit purposes and transition to a complete 64-bit platform. Underpinning this transition is Arm’s strategic framework, “Complete Compute Answer” (TCS), which revolves round three core rules: compute efficiency, safety, and developer entry. This strategy varieties the muse for Arm’s methodology and guides its efforts in delivering optimum efficiency, strong safety measures, and streamlined developer capabilities.

Arm’s deal with phasing out the 32-bit instruction set has been one it has been working in the direction of for a number of years. For his or her newest TCS23, they’ve lastly created a completely 64-bit cluster to capitalize on the advantage of an entire 64-bit cell ecosystem, excising AArch32 (32-bit instruction) help fully.. So whether or not it is a huge, mid, or little core, for Arm’s newest era of IP there’s solely AArch64.

Growing a dynamic system-on-a-chip (SoC) that caters to a broad spectrum of cell units, starting from cutting-edge flagship smartphones to entry-level fashions, necessitates a meticulous and constant strategy to sustaining competitiveness in a quickly increasing market. Within the realm of flagship units, as an example, Qualcomm’s Snapdragon 8 Gen2 SoC stands out, leveraging a cluster of Arm’s Cortex-X3, Cortex A715/710, and Cortex-A510 cores. The upcoming iteration of Qualcomm’s Snapdragon 8 Gen3 and different SoC producers are poised to harness the ability of Arm’s TSC23 core cluster and mental property to additional improve efficiency within the subsequent era of flagship cell units.

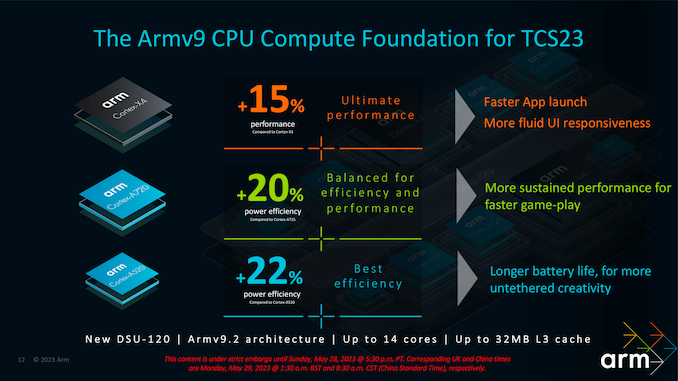

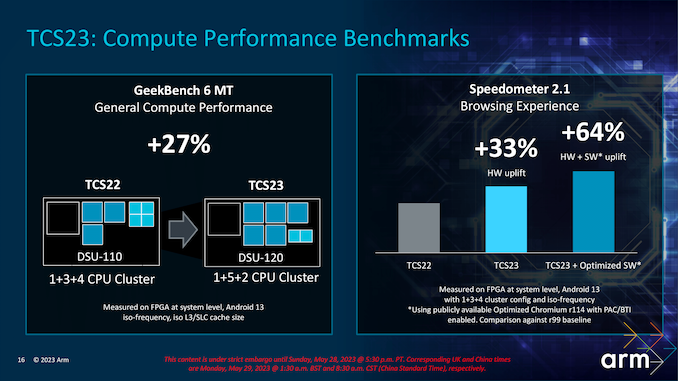

Arm’s newest DynamIQ Shared Unit, DSU-120, provides help for as much as 14 CPU cores in a cluster, which opens the door to a big variety of totally different CPU core mixtures. We’ll see what SoC distributors have opted for later this yr, however one most likely configuration is a 1+5+2 (X4+720+520), which is probably going a configuration for a high-end smartphone. In comparison with a last-generation 1+3+4 cluster (X3+715+510), Arm is claiming an uplift of 27% in compute efficiency inside GeekBench 6 MT and a extra appreciable uplift of between 33% and 64% within the Speedometer 2.1 benchmark relying on software program optimizations carried out.

Focusing extra on the strategy to 64-bit migration, final yr Arm introduced their first AArch64-only CPU core, the Cortex-A715. Consequently, final yr noticed the discharge of the primary 64-bit solely merchandise, resembling MediaTek’s Dimensity 9200 SoC, in addition to Google’s Pixel 7 – which was 64-bit solely as a platform alternative slightly than an architectural restriction.

That mentioned, precise AArch64 adoption/use inside the bigger software program ecosystem has been slower than anticipated, primarily because of the Chinese language market being gradual to make the change from 32-bit to 64-bit. Google has truly been key with its utility storage (Google Play) by requiring its builders to submit 64-bit apps way back to 2019, whereas additionally permitting using 32-bit purposes on units with out native 64-bit help. Different markets have not been as fast in doing so, however Arm claims that it’s ‘nudging’ corporations resembling OPPO, Vivi, and Xiaomi to undertake AArch64 sooner, which is believed to have the specified impact.

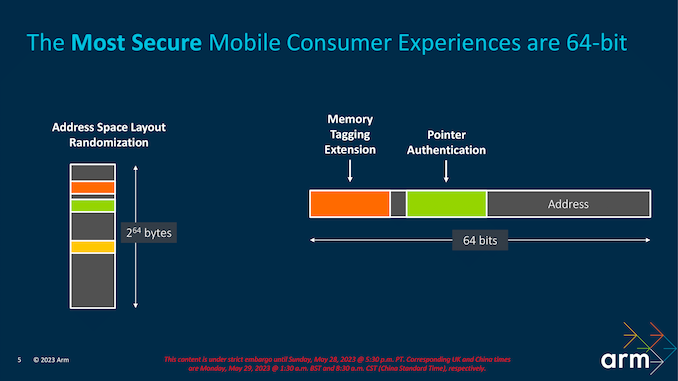

With the preliminary Armv9 structure, Arm made enhancements to safety via using its Reminiscence Tagging Extension (MTE) (Armv8.5), which is a hardware-based implementation that makes use of Pointer Authentication (PA) extensions to assist shield from reminiscence vulnerabilities. Reminiscence-based vulnerabilities have been a constant menace to hardware-based safety for a few years, and it’s one thing Arm is regularly growing inside its IP to assist mitigate all these assaults. For reference, Google’s Chromium Undertaking claimed that round 70% of high-severity bugs are from reminiscence.

One of many associated safety features of the newest Armv9.2 structure is the introduction of a brand new QARMA3 Pointer Authentication Code (PAC) algorithm. Arm claims the newer algorithm reduces the CPU overhead of PAC to lower than 1%, even on their little cores, giving builders and handset distributors even much less of a motive to not allow the safety function. Most of those enhancements revolve round {hardware} integrity and safety, with a mix of MTE and native advantages via the 64-bit instruction and structure, all designed to make units much more safe going into 2023 and past. This matches with Arm’s ethos to encourage a full change to 64-bit over a hybrid 64 and 32-bit market.

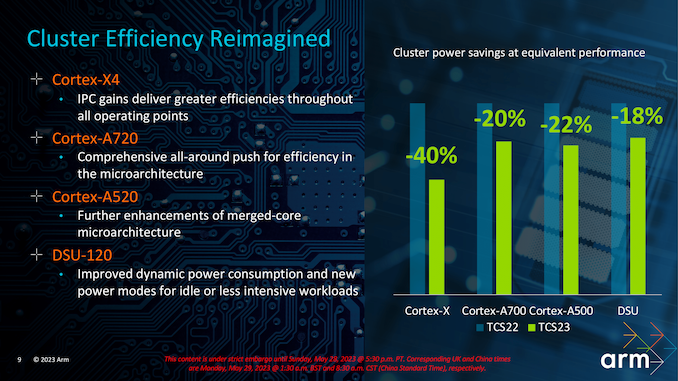

Lastly, taking a look at efficiency, Arm claims that their newest era CPU and core complicated structure has made stable positive factors in energy effectivity. At iso-performance, Cortex-X4 provides upwards of a 40% discount in energy consumption versus Cortex-X3, whereas Cortex-A720 and A520 save 20-22% over their respective predecessors. On the DSU-120 hub itself, Arm claims an 18% enchancment in energy effectivity.

In fact, most of those energy financial savings are going to as a substitute be invested in further efficiency. Nevertheless it goes to indicate what SoC and handset distributors can purpose for on this era in the event that they focus singularly on energy effectivity and battery life.