TSMC to Develop CoWoS Capability by 60% Yearly Via 2026

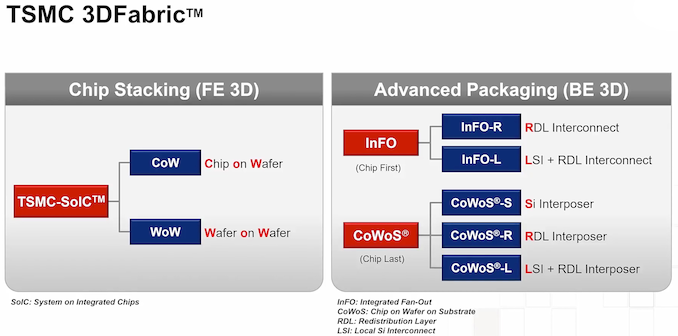

Buyer demand for AI and HPC processors is driving a a lot larger use of superior packaging applied sciences, significantly TSMC’s chip-on-wafer-on-substrate (CoWoS) companies. As issues stand, TSMC is simply barely assembly the present demand for this packaging technique – by no means thoughts future demand – which is why final yr the corporate introduced plans to greater than double CoWoS capability by the top of 2024. However because it seems, simply doubling capability as soon as will not be sufficient, and the world’s largest contract maker of chips goes to should maintain scaling up at a speedy tempo.

At its European Expertise Symposium final week TSMC introduced plans to broaden CoWoS capability at a compound annual progress charge (CAGR) of over 60% until not less than 2026. Consequently, TSMC’s CoWoS capability will greater than quadruple from 2023 ranges by the top of that interval. And maintaining in thoughts that TSMC is prepping extra variations of CoWoS (particularly CoWoS-L) that can allow constructing system-in-packages (SiPs) of up to eight reticle sizes, growing CoWoS capability by four-fold in three years could nonetheless not be sufficient. The excellent news is that the varied third-party off-site meeting and testing (OSAT) suppliers are additionally increasing their CoWoS-like capability, so the demand for superior packing is not an issue that TSMC is going through (or resolving) on their very own.

And CoWoS is not the one superior packaging know-how line whose capability TSMC is trying to quickly broaden. The corporate additionally has its system-on-integrated chips (SoIC) 3D stacking know-how which adoption is poised to develop within the coming years. To fulfill demand for its SoIC packaging strategies TSMC will broaden SoIC capability at a 100% compound annual progress charge by the top of 2026. Consequently, SoIC capability will develop by eight-fold from 2023 ranges by late 2026.

General, TSMC itself expects modern SiPs for demanding functions like AI and HPC will undertake each CoWoS and SoIC 3D stacking applied sciences within the coming years, which is why it wants to extend capability for each strategies to have the ability to construct these highly-complex processors.