Intel Broadens FPGA Vary with New Merchandise Throughout All Six FPGA Platforms

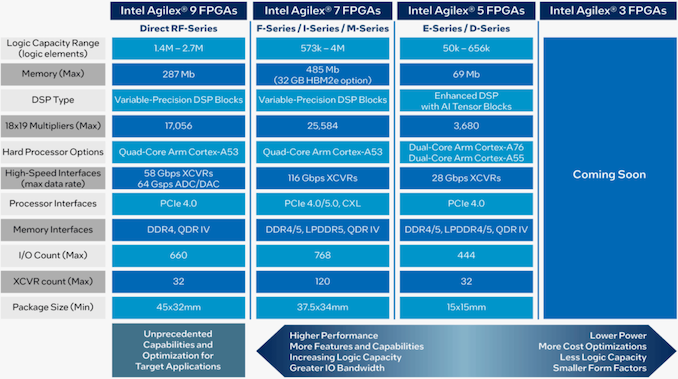

Intel’s Programmable Options Group (PSG) is broadening its FPGA product vary with the introduction of six new programmable platforms geared toward several types of clients and workloads. Along with a brand new sub-family of Agilex 5-series choices, Intel is launching its all-new Agilex 3 collection choices together with new Agilex.

The spotlight of right now’s announcement is the Intel Agilex 3 FPGA collection of energy and cost-optimized FPGAs in compact type components. The household contains the Agilex 3 B-series FPGAs that boast a better I/O density in compact type components (in comparison with Intel Max 10 FPGAs) and are optimized for board and system administration, together with server platform administration purposes.

On the opposite facet of the Agilex 3 spectrum is the C-series FPGAs which can be engineered to supply supplementary capabilities, making them apt for a broad spectrum of complicated programmable logic gadgets (CPLD) and FPGA purposes throughout numerous industries. Intel says that its Agilex 3-series FPGAs will likely be out there quickly with out disclosing when precisely.

One other noteworthy introduction is the Intel Agilex 5 FPGA E-series primarily based on the twond Era Hyperflex FPGA structure and tailor-made for embedded edge purposes and due to this fact that includes excessive efficiency effectivity. Intel produces these FPGAs in home utilizing its Intel 7 manufacturing know-how (previously often known as 10 nm Enhanced SuperFin), which is why it says that these elements ship 1.6 instances larger efficiency per watt in comparison with competing FPGAs made on a 16 nm-class course of know-how (presumably referring to Xilinx’s FPGAs constructed on this course of node). Moreover, this FPGA collection integrates an AI tensor block, a function beforehand unique to Intel’s premium programmable elements, positioning it as an answer for edge AI duties. Intel will begin sampling Agilex 5 E-series elements with design software program in Q1 2024. A system simulator for these FPGAs will likely be out there within the cloud in late 2024.

Intel additionally mentioned that it had begun shipments of its Intel Agilex 7 FPGAs with the R-Tile chiplet. These FPGAs provide a PCIe 5.0 interface with the CXL protocol on high that enable to shortly deploy programmable accelerators for particular duties that may profit from larger bandwidth and decrease latencies.

Along with revealing new FPGAs, Intel additionally mentioned that the primary industrial product primarily based on its F2000X infrastructure processing unit platform is now delivery. The half is the Napatech F2070X IPU that has two 100 GbE ports and is powered by the Agilex AGFC023 FPGA and an Intel Xeon D SoC.

Rounding off the brand new introductions is the Nios V/c compact microcontroller, which is a soft-core IP, primarily based on the RISC-V structure, which might be programmed utilizing the corporate’s Quartus Prime Professional software program.