TSMC Readies 8x Reticle Tremendous Provider Interposer For Subsequent-Gen Chips Twice as Giant As At present’s

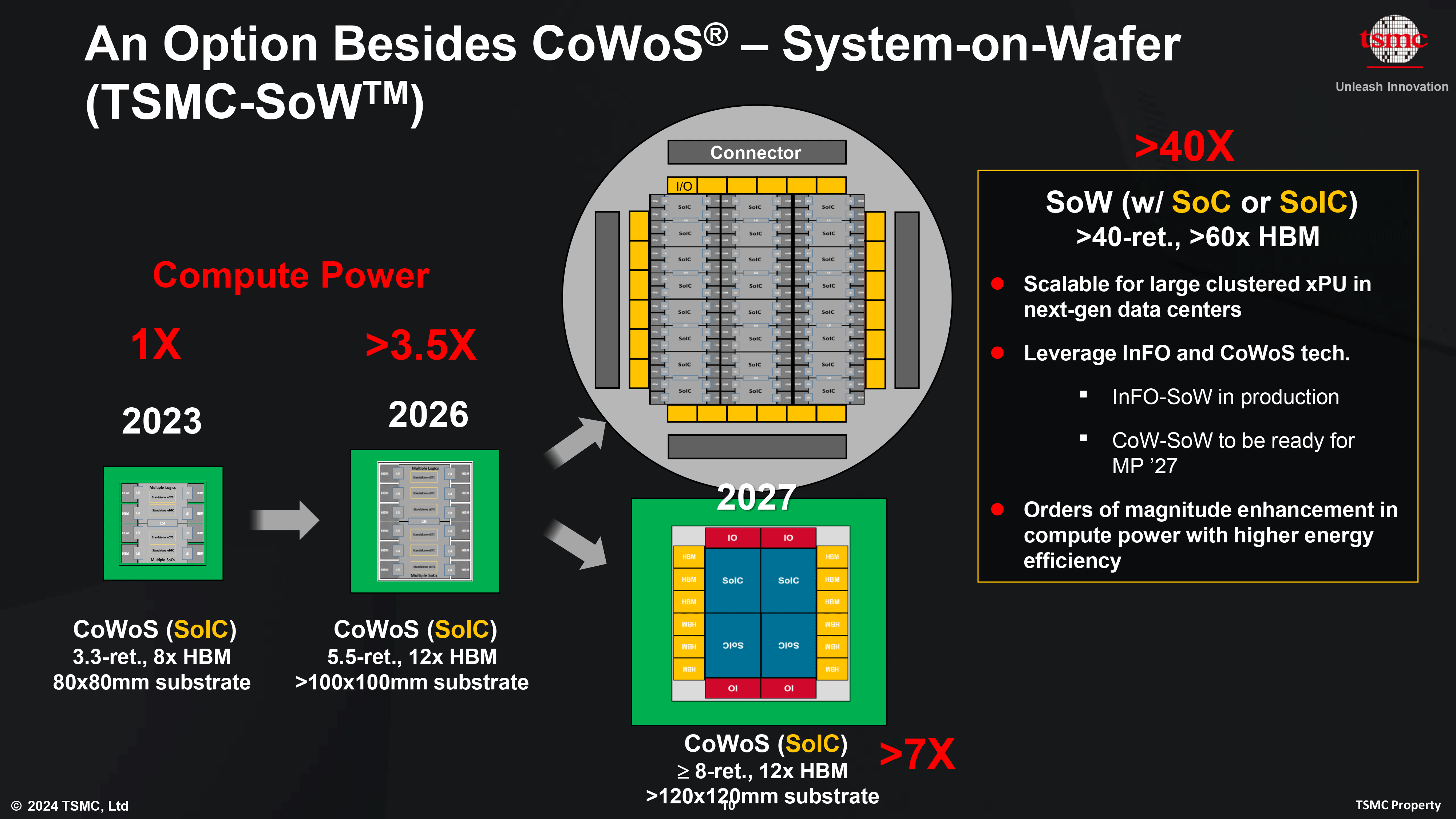

TSMC isn’t any stranger to constructing huge chips. Apart from the ~800mm2 reticle restrict of their regular logic processes, the corporate already produces even bigger chips by becoming a number of dies on to a single silicon interposer, utilizing their chip-on-wafer-on-substrate (CoWoS) expertise. However even with current-gen CoWoS permitting for interposers as much as 3.3x TSMC’s reticle restrict, TSMC plans to construct larger nonetheless in response to projected demand from the HPC and AI industries. To that finish, as a part of the corporate’s North American Know-how Symposium final week, TSMC introduced that they’re creating the technique of constructing super-sized interposers that may attain over 8x the reticle restrict.

TSMC’s current-generation CoWoS expertise permits for constructing interposers as much as 2831 mm2 and the corporate is already seeing prospects are available in with designs that run as much as these limits. Each AMD’s Intuition MI300X accelerator and NVIDIA’s forthcoming B200 accelerator are prime examples of this, as they pack enormous logic chiplets (3D stacked in case of AMD’s product) and eight HBM3/HBM3E reminiscence stacks in whole. The overall house afforded by the interposer offers these processors formidable efficiency, however chip builders wish to go extra highly effective nonetheless. And to get there as shortly as potential, they will must go larger as nicely so as to incorporate extra logic chiplets and extra reminiscence stacks.

For his or her next-generation CoWoS product that is set to launch in 2026, TSMC plans to launch CoWoS_L, which can provide a most interposer dimension of roughly 5.5 occasions that of a photomask, totaling 4719 mm² altogether. This subsequent technology package deal will help as much as 12 HBM reminiscence stacks and can necessitate a bigger substrate measuring at 100×100 mm. Coupled with course of node enhancements over the following few years, and TSMC expects chips based mostly on this technology of CoWoS to supply higher than 3.5x the compute efficiency of current-generation CoWoS chips.

Farther down the road, in 2027 TSMC intends introduce a model of CoWoS that enables for interposers as much as 8 occasions bigger than the reticle restrict. This may provide an ample 6,864 mm² of house for chiplets on a substrate that measures 120×120 mm. TSMC envisions leveraging this expertise for designs that combine 4 stacked systems-on-integrated chips (SoICs), with 12 HBM4 reminiscence stacks and further I/O dies. TSMC roughly initiatives that it will allow chip designers to as soon as once more double efficiency, producing chips that surpass 7x the efficiency of current-generation chips.

In fact, constructing such giant chips will include its personal set of penalties, above and past what TSMC must cope with. Enabling chip designers to construct such grand processors goes to influence system design, in addition to how datacenters accommodate these techniques. TSMC’s 100×100mm substrate shall be driving proper as much as the restrict of the OAM 2.0 type issue, whose modules measure 102×165mm to start with. And if that technology of CoWoS does not break the present OAM type issue, then 120×120mm chips actually will. And, in fact, all of that additional silicon requires extra energy and cooling, which is why we’re already seeing {hardware} distributors put together for the best way to cool multi-kilowatt chips by investigating liquid and immersion cooling.

In the end, even when Moore’s Legislation has slowed to a crawl by way of delivering transistor density enhancements, CoWoS presents an out for producing chips with an ever-larger variety of transistors. So with TSMC set to supply interposers and substrates with over twice the realm of right now’s options, huge chips meant for HPC techniques are solely going to proceed to develop in each efficiency and dimension.