PCI-SIG Demonstrates PCIe 6.0 Interoperability at FMS 2024

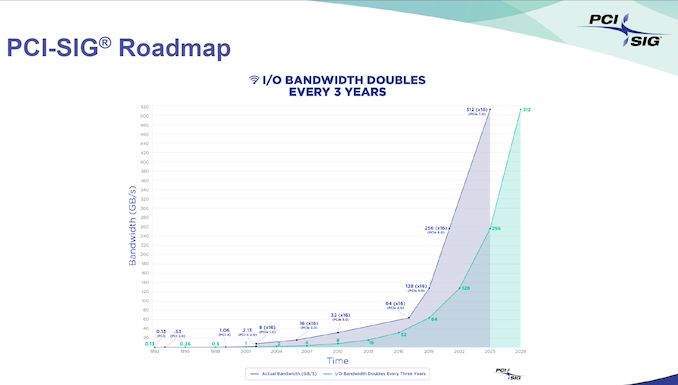

Because the deployment of PCIe 5.0 picks up steam in each datacenter and client markets, PCI-SIG isn’t sitting idle, and is already engaged on getting the ecosystem prepared for the updats to the PCIe specs. At FMS 2024, some distributors had been even speaking about PCIe 7.0 with its 128 GT/s capabilities regardless of PCIe 6.0 not even beginning to ship but. We caught up with PCI-SIG to get some updates on its actions and have a dialogue on the present state of the PCIe ecosystem.

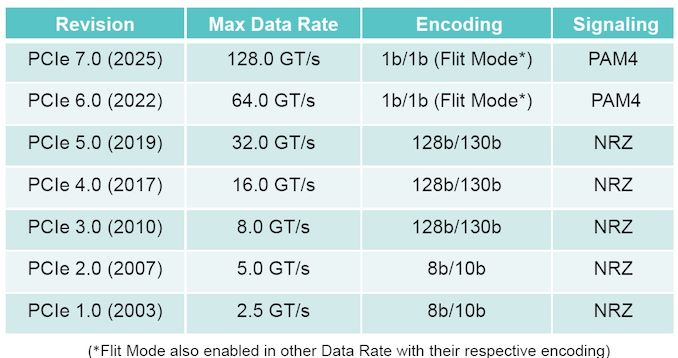

PCI-SIG has already made the PCIe 7.0 specs (v 0.5) accessible to its members, and expects full specs to be formally launched someday in 2025. The objective is to ship a 128 GT/s information charge with as much as 512 GBps of bidirectional visitors utilizing x16 hyperlinks. Much like PCIe 6.0, this specification may even make the most of PAM4 signaling and keep backwards compatibility. Energy effectivity in addition to silicon die space are additionally being saved in thoughts as a part of the drafting course of.

The transfer to PAM4 signaling brings greater bit-error charges in comparison with the earlier NRZ scheme. This made it essential to undertake a unique error correction scheme in PCIe 6.0 – as an alternative of working on variable size packets, PCIe 6.0’s Move Management Unit (FLIT) encoding operates on fastened measurement packets to assist in ahead error correction. PCIe 7.0 retains these features.

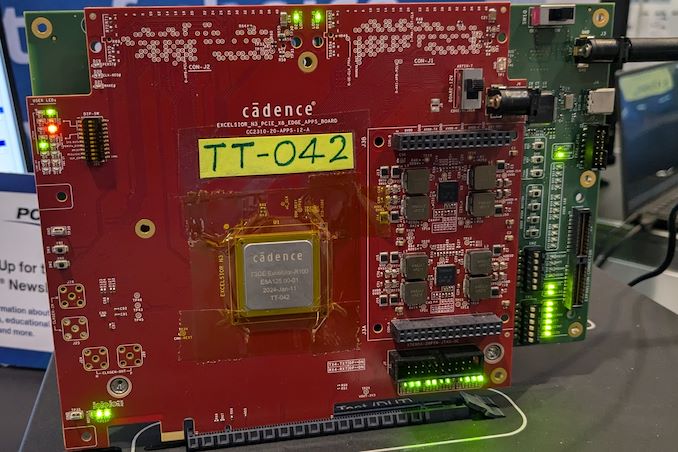

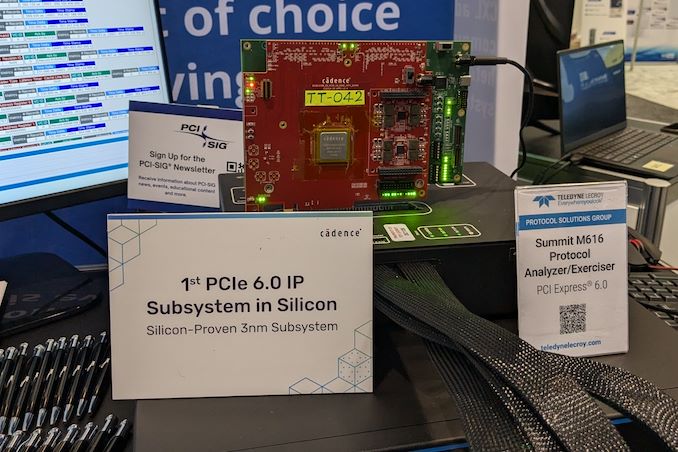

The integrators listing for the PCIe 6.0 compliance program can also be anticipated to come back out in 2025, although preliminary testing is already in progress. This was evident by the FMS 2024 demo involving Cadence’s 3nm take a look at chip for its PCIe 6.0 IP providing together with Teledyne Lecroy’s PCIe 6.0 analyzer. These timelines monitor nicely with the specification completion dates and compliance program availability for earlier PCIe generations.

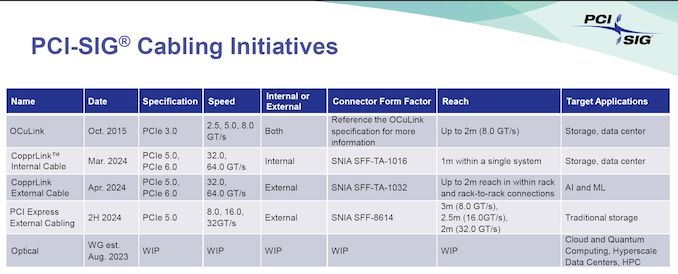

We additionally obtained an replace on the optical workgroup – whereas being optical-technology agnostic, the WG additionally intends to develop technology-specific form-factors together with pluggable optical transceivers, on-board optics, co-packaged optics, and optical I/O. The logical and electrical layers of the PCIe 6.0 specs are being enhanced to accommodate the brand new optical PCIe standardization and this course of may even be completed with PCIe 7.0 to coincide with that normal’s launch subsequent 12 months.

The PCI-SIG additionally has ongoing cabling initiatives. On the patron aspect, we have now seen vital traction for Thunderbolt and exterior GPU enclosures. Nevertheless, even datacenters and enterprise techniques are transferring in direction of cabling options because it turns into evident that disaggregation of parts similar to storage from the CPU and GPU are higher for thermal design. Moreover sustaining sign integrity over longer distances turns into troublesome for on-board sign traces. Cabling inner to the computing techniques can assist right here.

OCuLink emerged as a very good candidate and was adopted pretty broadly as an inner hyperlink in server techniques. It has even made an look in mini-PCs from some Chinese language producers in its exterior avatar for the patron market, albeit with restricted traction. As speeds improve, a widely-adopted normal for exterior PCIe peripherals (and even connecting parts inside a system) will change into crucial.