Developments in machine studying for machine studying – Google Analysis Weblog

With the latest and accelerated advances in machine studying (ML), machines can understand natural language, engage in conversations, draw images, create videos and extra. Fashionable ML fashions are programmed and educated utilizing ML programming frameworks, akin to TensorFlow, JAX, PyTorch, amongst many others. These libraries present high-level directions to ML practitioners, akin to linear algebra operations (e.g., matrix multiplication, convolution, and so on.) and neural community layers (e.g., 2D convolution layers, transformer layers). Importantly, practitioners needn’t fear about methods to make their fashions run effectively on {hardware} as a result of an ML framework will robotically optimize the person’s mannequin by way of an underlying compiler. The effectivity of the ML workload, thus, will depend on how good the compiler is. A compiler sometimes depends on heuristics to resolve complicated optimization issues, usually leading to suboptimal efficiency.

On this weblog publish, we current thrilling developments in ML for ML. Particularly, we present how we use ML to enhance effectivity of ML workloads! Prior works, each inner and exterior, have proven that we will use ML to enhance efficiency of ML packages by deciding on higher ML compiler choices. Though there exist just a few datasets for program efficiency prediction, they aim small sub-programs, akin to fundamental blocks or kernels. We introduce “TpuGraphs: A Performance Prediction Dataset on Large Tensor Computational Graphs” (introduced at NeurIPS 2023), which we just lately launched to gasoline extra analysis in ML for program optimization. We hosted a Kaggle competition on the dataset, which just lately accomplished with 792 contributors on 616 groups from 66 nations. Moreover, in “Learning Large Graph Property Prediction via Graph Segment Training”, we cowl a novel technique to scale graph neural network (GNN) coaching to deal with giant packages represented as graphs. The approach each permits coaching arbitrarily giant graphs on a tool with restricted reminiscence capability and improves generalization of the mannequin.

ML compilers

ML compilers are software program routines that convert user-written packages (right here, mathematical directions supplied by libraries akin to TensorFlow) to executables (directions to execute on the precise {hardware}). An ML program may be represented as a computation graph, the place a node represents a tensor operation (akin to matrix multiplication), and an edge represents a tensor flowing from one node to a different. ML compilers have to resolve many complicated optimization issues, together with graph-level and kernel-level optimizations. A graph-level optimization requires the context of all the graph to make optimum choices and transforms all the graph accordingly. A kernel-level optimization transforms one kernel (a fused subgraph) at a time, independently of different kernels.

|

| Vital optimizations in ML compilers embrace graph-level and kernel-level optimizations. |

To supply a concrete instance, think about a matrix (2D tensor):

|

It may be saved in pc reminiscence as [A B C a b c] or [A a B b C c], generally known as row- and column-major memory layout, respectively. One essential ML compiler optimization is to assign reminiscence layouts to all intermediate tensors in this system. The determine beneath reveals two totally different structure configurations for a similar program. Let’s assume that on the left-hand aspect, the assigned layouts (in crimson) are essentially the most environment friendly possibility for every particular person operator. Nevertheless, this structure configuration requires the compiler to insert a copy operation to rework the reminiscence structure between the add and convolution operations. Then again, the right-hand aspect configuration is likely to be much less environment friendly for every particular person operator, but it surely doesn’t require the extra reminiscence transformation. The structure task optimization has to commerce off between native computation effectivity and structure transformation overhead.

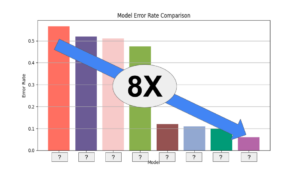

If the compiler makes optimum selections, vital speedups may be made. For instance, we now have seen up to a 32% speedup when selecting an optimum structure configuration over the default compiler’s configuration within the XLA benchmark suite.

TpuGraphs dataset

Given the above, we intention to enhance ML mannequin effectivity by bettering the ML compiler. Particularly, it may be very efficient to equip the compiler with a learned cost model that takes in an enter program and compiler configuration after which outputs the anticipated runtime of this system.

With this motivation, we release TpuGraphs, a dataset for studying value fashions for packages operating on Google’s customized Tensor Processing Units (TPUs). The dataset targets two XLA compiler configurations: structure (generalization of row- and column-major ordering, from matrices, to larger dimension tensors) and tiling (configurations of tile sizes). We offer obtain directions and starter code on the TpuGraphs GitHub. Every instance within the dataset accommodates a computational graph of an ML workload, a compilation configuration, and the execution time of the graph when compiled with the configuration. The graphs within the dataset are collected from open-source ML packages, that includes well-liked mannequin architectures, e.g., ResNet, EfficientNet, Mask R-CNN, and Transformer. The dataset supplies 25× extra graphs than the most important (earlier) graph property prediction dataset (with comparable graph sizes), and graph measurement is 770× bigger on common in comparison with current efficiency prediction datasets on ML packages. With this drastically expanded scale, for the primary time we will discover the graph-level prediction process on giant graphs, which is topic to challenges akin to scalability, coaching effectivity, and mannequin high quality.

|

| Scale of TpuGraphs in comparison with different graph property prediction datasets. |

We offer baseline discovered value fashions with our dataset (structure proven beneath). Our baseline fashions are based mostly on a GNN for the reason that enter program is represented as a graph. Node options, proven in blue beneath, include two components. The primary half is an opcode id, an important data of a node, which signifies the kind of tensor operation. Our baseline fashions, thus, map an opcode id to an opcode embedding by way of an embedding lookup desk. The opcode embedding is then concatenated with the second half, the remainder of the node options, as inputs to a GNN. We mix the node embeddings produced by the GNN to create the fixed-size embedding of the graph utilizing a easy graph pooling discount (i.e., sum and imply). The ensuing graph embedding is then linearly remodeled into the ultimate scalar output by a feedforward layer.

|

| Our baseline discovered value mannequin employs a GNN since packages may be naturally represented as graphs. |

Moreover we current Graph Segment Training (GST), a way for scaling GNN coaching to deal with giant graphs on a tool with restricted reminiscence capability in circumstances the place the prediction process is on the entire-graph (i.e., graph-level prediction). Not like scaling coaching for node- or edge-level prediction, scaling for graph-level prediction is understudied however essential to our area, as computation graphs can include lots of of 1000’s of nodes. In a typical GNN coaching (“Full Graph Coaching”, on the left beneath), a GNN mannequin is educated utilizing a complete graph, that means all nodes and edges of the graph are used to compute gradients. For giant graphs, this is likely to be computationally infeasible. In GST, every giant graph is partitioned into smaller segments, and a random subset of segments is chosen to replace the mannequin; embeddings for the remaining segments are produced with out saving their intermediate activations (to keep away from consuming reminiscence). The embeddings of all segments are then mixed to generate an embedding for the unique giant graph, which is then used for prediction. As well as, we introduce the historic embedding desk to effectively receive graph segments’ embeddings and phase dropout to mitigate the staleness from historic embeddings. Collectively, our full technique accelerates the end-to-end coaching time by 3×.

|

| Evaluating Full Graph Coaching (typical technique) vs Graph Section Coaching (our proposed technique). |

Kaggle competitors

Lastly, we ran the “Fast or Slow? Predict AI Model Runtime” competitors over the TpuGraph dataset. This competitors ended with 792 contributors on 616 groups. We had 10507 submissions from 66 nations. For 153 customers (together with 47 within the prime 100), this was their first competitors. We discovered many attention-grabbing new strategies employed by the collaborating groups, akin to:

- Graph pruning / compression: As an alternative of utilizing the GST technique, many groups experimented with other ways to compress giant graphs (e.g., conserving solely subgraphs that embrace the configurable nodes and their speedy neighbors).

- Characteristic padding worth: Some groups noticed that the default padding worth of 0 is problematic as a result of 0 clashes with a legitimate characteristic worth, so utilizing a padding worth of -1 can enhance the mannequin accuracy considerably.

- Node options: Some groups noticed that further node options (akin to dot general’s contracting dimensions) are essential. A couple of groups discovered that totally different encodings of node options additionally matter.

- Cross-configuration consideration: A successful crew designed a easy layer that permits the mannequin to explicitly “examine” configs in opposition to one another. This method is proven to be significantly better than letting the mannequin infer for every config individually.

We are going to debrief the competitors and preview the successful options on the competitors session on the ML for Systems workshop at NeurIPS on December 16, 2023. Lastly, congratulations to all of the winners and thanks on your contributions to advancing analysis in ML for methods!

NeurIPS expo

In case you are thinking about extra analysis about structured information and synthetic intelligence, we hosted the NeurIPS Expo panel Graph Learning Meets Artificial Intelligence on December 9, which lined advancing discovered value fashions and extra!

Acknowledgements

Sami Abu-el-Haija (Google Analysis) contributed considerably to this work and write-up. The analysis on this publish describes joint work with many further collaborators together with Mike Burrows, Kaidi Cao, Bahare Fatemi, Jure Leskovec, Charith Mendis, Dustin Zelle, and Yanqi Zhou.